JTAG (Joint Test Action Group) dobro je uspostavljen standard IEEE 1149.1 koji je razvijen 1980. godine za rješavanje proizvodnih problema koji su se javljali unutar elektroničkih ploča ili tiskane ploče . Ova se tehnologija koristi za pružanje dovoljnog testnog pristupa za svaku složenu ploču kada se testni pristup smanjivao. Tako je pokrenuta tehnologija graničnog skeniranja i JTAG standard ili JTAG specifikacija se uspostavlja. Složenost elektronike raste iz dana u dan, tako da je JTAG specifikacija postala prihvaćeni testni format za testiranje kompliciranih i kompaktnih elektroničkih jedinica. Ovaj članak govori o pregledu a JTAG protokol – rad s aplikacijama.

Što je JTAG?

Naziv koji je dan IEEE 1149.1 Standard Test Access Portu kao i Boundary-Scan Architecture poznat je kao JTAG (Joint Test Action Group). Ova arhitektura graničnog skeniranja uglavnom se koristi unutar računala procesori jer je prvi procesor s JTAG-om izdao Intel. Ovaj IEEE standard jednostavno definira kako se strujni krug računala testira kako bi se potvrdilo radi li ispravno nakon postupka proizvodnje. Na sklopnim pločama provode se testovi za provjeru lemljenih spojeva.

Joint Test Action Group pruža pregled pinova za testere sa svakom IC pločicom što pomaže u prepoznavanju bilo kakvih grešaka unutar sklopovske ploče. Nakon što se ovaj protokol poveže s čipom, to može priključiti sondu na čip dopuštajući razvojnom programeru da kontrolira čip kao i njegove veze s drugim čipovima. Programeri također mogu koristiti sučelje s grupom Joint Test Action za kopiranje firmvera u trajnu memoriju u elektroničkom uređaju.

Konfiguracija/Pin Out

Skupina za zajedničku akciju testiranja uključuje 20 pinova gdje se o svakom pinu i njegovoj funkciji govori u nastavku.

Pin1 (VTref): Ovo je pin ciljanog referentnog napona koji se koristi za spajanje na glavno napajanje cilja koje se kreće od 1,5 do 5,0 VDC.

Pin2 (Vnapajanje): Ovo je ciljani napon napajanja koji se koristi za spajanje glavnog napona napajanja ciljnih 1,5 VDC – 5,0 VDC.

Pin3 (nTRST): Ovo je testni pin za resetiranje koji se koristi za resetiranje stanja automata TAP kontrolera.

Pinovi (4, 6, 8, 10, 12, 14, 16, 18 i 20): Ovo su uobičajeni GND kontakti.

Pin5 (TDI): Ovo su testni podaci u pribadači. Ovi se podaci prebacuju u ciljni uređaj. Ova se igla mora podići prema definiranom stanju na ciljnoj ploči.

Pin7 (TMS): Ovo je pin stanja testnog načina rada koji se povlači kako bi se odredilo sljedeće stanje stroja stanja TAP kontrolera.

Pin9 (TCK): Ovo je pin testnog sata koji sinkronizira operacije unutarnjeg stroja stanja u TAP kontroleru.

Pin11 (RTCK): Ovo je input Return TCK pin koji se koristi u uređajima koji podržavaju adaptivno taktiranje.

Pin13 (TDO): Ovo je igla Test Data Out, tako da se podaci premještaju iz ciljnog uređaja u Flyswatter.

Pin15 (nSRST): Ovo je pin za resetiranje ciljnog sustava koji je povezan s glavnim signalom za resetiranje mete.

Pinovi 17 i 19 (NC): Ovo nisu povezani pinovi.

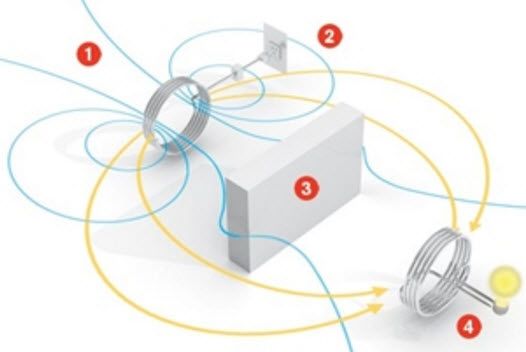

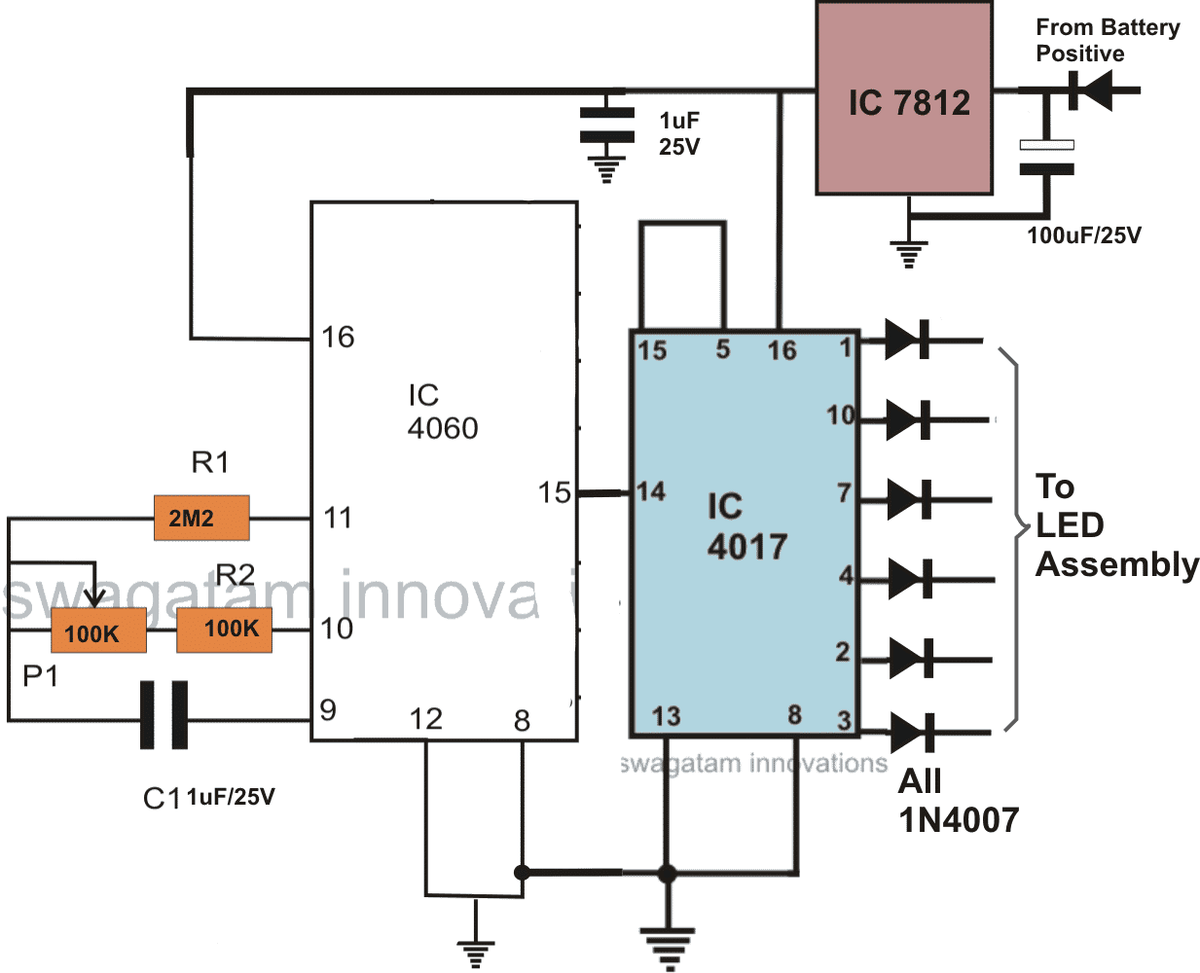

JTAG radi

Izvorna upotreba JTAG-a je za testiranje granica. Ovdje je jednostavna tiskana ploča koja uključuje dva IC-a kao što su CPU i FPGA . Tipična ploča može uključivati mnogo IC-ova. Općenito, IC-ovi uključuju mnogo pinova koji su međusobno povezani s mnogo priključaka. Ovdje, u sljedećem dijagramu, prikazana su samo četiri priključka.

Dakle, ako dizajnirate mnogo ploča gdje svaka ploča ima tisuće veza. U tome ima loših ploča. Dakle, moramo provjeriti koja ploča radi, a koja ne radi. Za to je osmišljena Joint Test Action Group.

Ovaj protokol može koristiti kontrolne pinove svih čipova, ali u sljedećem dijagramu, Joint Test Action Group će napraviti sve izlazne pinove CPU-a i sve ulazne pinove FPGA. Nakon toga, odašiljanjem određene količine podataka s pinova CPU-a i čitanjem vrijednosti pinova s FPGA, JTAG izjavljuje da su spojevi PCB ploče u redu.

Zapravo, Joint Test Action Group uključuje četiri logička signala TDI, TDO, TMS i TCK. I ti signali moraju biti povezani na poseban način. U početku, TMS i TCK su spojeni paralelno na sve IC-ove JTAG-a.

Nakon toga, i TDI i TDO su povezani za formiranje lanca. Kao što možete primijetiti, svaki JTAG kompatibilan IC uključuje 4 pina koji se koriste za JTAG gdje su 3 pina ulazi, a 4. pin je izlaz. Peti pin kao TRST nije obavezan. Obično se JTAG pinovi ne dijele u druge svrhe.

Korištenjem Joint Test Action Group, svi IC-ovi koriste granično testiranje za koje je izvorni razlog kreirao JTAG. Trenutačno je upotreba ovog protokola proširena kako bi se omogućile različite stvari poput konfiguracije FPGA-a, a nakon toga JTAG se koristi u FPGA jezgri za potrebe otklanjanja pogrešaka.

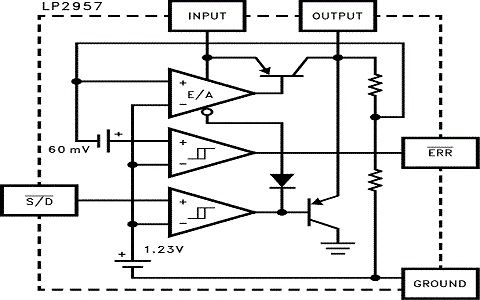

JTAG arhitektura

JTAG arhitektura prikazana je u nastavku. U ovoj arhitekturi, svi signali između jezgrene logike uređaja i pinova se prekidaju kroz serijski put skeniranja koji se naziva BSR ili registar graničnog skeniranja. Ovaj BSR uključuje razne 'stanice' graničnog skeniranja. Općenito, ove ćelije graničnog skeniranja nisu vidljive, ali se mogu koristiti za postavljanje ili očitavanje vrijednosti unutar načina testiranja s pinova uređaja.

JTAG sučelje nazvano TAP ili Test Access Port koristi različite signale za podršku operaciji graničnog skeniranja kao što su TCK, TMS, TDI, TDO i TRST.

- TCK ili Test Clock signal jednostavno sinkronizira unutarnje operacije stroja stanja.

- TMS ili Test Mode Select signal uzorkuje se na rastućem rubu signala testnog takta za odlučivanje o sljedećem stanju.

- TDI ili Test Data In signal označava pomaknute podatke u testni uređaj inače logiku programiranja. Jednom kada je stroj unutarnjeg stanja u ispravnom stanju tada se uzorkuje na rastućem rubu TCK.

- TDO ili izlazni signal testnih podataka označava pomaknute podatke testnog uređaja inače programskom logikom. Jednom kada je stroj unutarnjeg stanja u ispravnom stanju tada je važeći na opadajućem rubu TCK

- TRST ili Test Reset je dodatni pin koji se koristi za resetiranje stanja automata TAP kontrolera.

TAP kontroler

Testna pristupna točka u arhitekturi JTAG sastoji se od TAP kontrolera, registra instrukcija i registara testnih podataka. Ovaj kontroler uključuje automat za testiranje koji je odgovoran za čitanje TMS & TCK signala. Ovdje se podatkovni i/p pin jednostavno koristi za učitavanje podataka u granične ćelije između IC jezgre i fizičkih pinova, te za učitavanje podataka u jedan od registara podataka ili u registar instrukcija. Podatkovni o/p pin se koristi za čitanje podataka iz registara ili graničnih ćelija.

Strojem stanja TAP kontrolera upravlja TMS, a taktira ga TCK. Državni stroj koristi dvije staze za označavanje dva različita načina rada kao što su način rada s uputama i način rada s podacima.

Registri

Postoje dvije vrste registara dostupnih unutar graničnog skeniranja. Svaki sukladan uređaj uključuje najmanje dva ili više registara podataka i jedan registar instrukcija.

Registar uputa

Registar instrukcija se koristi za čuvanje trenutne instrukcije. Dakle, njegove podatke koristi TAP kontroler da odluči što će izvršiti sa signalima koji se dobiju. Najčešće će podaci registra instrukcija opisati u koji od registara podataka signali moraju biti proslijeđeni.

Registri podataka

Registri podataka dostupni su u tri tipa BSR (registar graničnog skeniranja), BYPASS i registar ID KODOVA. Također, mogu postojati i drugi registri podataka, no oni nisu nužni kao element JTAG standarda.

Registar graničnog skeniranja (BSR)

BSR je glavni registar podataka za testiranje koji se koristi za prebacivanje podataka s i na I/O pinove uređaja.

ZAOBIĆI

Premosnica je jednobitni registar koji se koristi za prijenos podataka iz TDI – TDO. Tako omogućuje testiranje dodatnih uređaja unutar strujnog kruga uz minimalno opterećenje.

ID KODOVI

Ova vrsta registra podataka uključuje ID kod kao i revizijski broj za uređaj. Dakle, ovi podaci omogućuju da se uređaj poveže sa svojom BSDL (Boundary Scan Description Language) datotekom. Ova je datoteka uključivala pojedinosti o konfiguraciji graničnog skeniranja za uređaj.

Rad JTAG-a je, u početku, način rada instrukcija gdje jedno od stanja u ovom načinu 'staza' dopušta operateru da sat unutar instrukcije putem TDI-ja. Nakon toga se državni stroj razvija dok se ne preuredi. Sljedeći korak za većinu uputa je odabir podatkovnog načina. Dakle, u ovom načinu rada podaci se učitavaju kroz TDI za čitanje iz TDO-a. Za TDI & TDO, putevi podataka bit će raspoređeni u skladu s uputama koje su učitane. Nakon što je operacija čitanja/pisanja obavljena, stroj stanja ponovno se razvija u stanje resetiranja.

Razlika između JTAG-a i UART-a

Razlika između JTAG-a i UART-a uključuje sljedeće.

| JTAG |

UART |

| Izraz 'JTAG' označava Joint Test Action Group. | Uvjet ' UART ” označava univerzalni asinkroni prijemnik/odašiljač. |

| To je sinkrono sučelje koje koristi ugrađeni hardver za programiranje bljeskalice . | UART je asinkrono sučelje koje koristi bootloader koji radi unutar memorije. |

| To je skup testnih priključaka koji se koriste za otklanjanje pogrešaka, ali se također mogu koristiti za programiranje firmvera (što se obično radi).

|

UART je vrsta čipa koji kontrolira komunikaciju prema i od uređaja, kao što je mikrokontroler, ROM, RAM, itd. Većinu vremena, to je serijska veza koja nam omogućuje komunikaciju s uređajem. |

| Dostupni su u četiri vrste TDI, TDO, TCK, TMS i TRST. | Dostupni su u dvije vrste dumb UART & FIFO UART. |

| Joint Test Action Group je protokol za serijsko programiranje ili pristup podacima koji se koristi u sučelju mikrokontrolera i srodnih uređaja. | UART je jedna vrsta čipa inače podkomponente mikrokontrolera koja se koristi za pružanje hardvera za generiranje asinkronog serijskog toka kao što je RS-232/RS-485. |

| JTAG komponente su procesori, FPGA, CPLD-ovi , itd. | Komponente UART-a su CLK generator, I/O registri posmaka, međuspremnici prijenosa ili primanja, međuspremnik sabirnice podataka sustava, kontrolna logika čitanja ili pisanja, itd. |

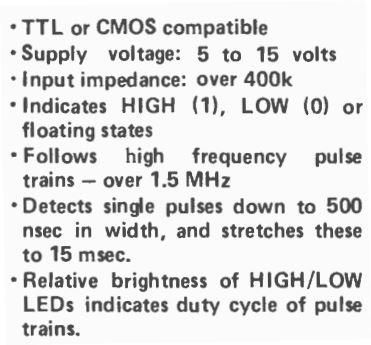

JTAG analizator protokola

JTAG analizator protokola kao što je PGY-JTAG-EX-PD jedna je vrsta analizatora protokola koji uključuje neke značajke za snimanje i otklanjanje pogrešaka u komunikaciji između glavnog računala i dizajna koji se testira. Ova vrsta analizatora vodeći je instrument koji inženjerima za testiranje i dizajn omogućuje testiranje određenih dizajna JTAG-a za njegove specifikacije putem raspoređivanja PGY-JTAG-EX-PD kao Master ili Slave za generiranje JTAG prometa i dekodiranje dekodiranih paketa Protokol zajedničke ispitne akcijske skupine.

Značajke

Značajke JTAG analizatora protokola uključuju sljedeće.

- Podržava do 25MH JTAG frekvencija.

- Generira JTAG promet i dekodiranje protokola za sabirnicu istovremeno.

- Ima JTAG Master Capability.

- Varijabilne JTAG brzine podataka i radni ciklus.

- Korisnički definirana kašnjenja TDI i TCK.

- USB 2.0 ili 3.0 sučelje glavnog računala.

- Analiza pogrešaka unutar dekodiranja protokola

- Protokolom dekodirani vremenski dijagram sabirnice.

- Kontinuirani protok podataka protokola na glavno računalo radi pružanja velikog međuspremnika.

- Popis aktivnosti protokola.

- Različitim brzinama može se napisati skripta vježbe za kombiniranje višestrukog generiranja okvira podataka.

Vremenski dijagram

The vremenski dijagram JTAG-a protokol je prikazan u nastavku. U sljedećem dijagramu TDO pin ostaje unutar uvjeta visoke impedancije osim tijekom stanja shift-IR/shift-DR kontrolera.

U uvjetima kontrolera shift-IR & Shift-DR, TDO pin se ažurira na opadajućem rubu TCK kroz Target i uzorkuje na rastućem rubu TCK kroz Host.

I TDI i TMS pinovi se jednostavno uzorkuju na rastućem rubu TCK kroz Target. Ažurirano na opadajućem rubu inače TCK putem hosta.

Prijave

The JTAG aplikacije uključuju sljedeće.

- Joint Test Action Group često se koristi u procesorima za pružanje prava pristupa njihovim funkcijama emulacije ili otklanjanja pogrešaka.

- Svi CPLD i FPGA koriste ovo kao sučelje za pristup svojim programskim funkcijama.

- Koristi se za testiranje PCB-a bez fizičkog pristupa

- Koristi se za testove proizvodnje na razini ploče.

Dakle, ovo je sve o tome pregled JTAG-a – konfiguracija pinova, rad s aplikacijama. Industrijski standard JTAG koristi se za provjeru dizajna kao i za testiranje PCB-a nakon proizvodnje. Evo pitanja za vas, JTAG je kratica za?