Ovaj članak objašnjava generiranje modulacije širine impulsa signali s promjenjivim radnim ciklusom na FPGA pomoću VHDL-a. PWM ima fiksnu frekvenciju i promjenjivi napon. Ovaj članak također govori o Upravitelju digitalnih satova za smanjenje frekvencije takta smanjenjem iskrivljenosti signala sata. Fiksna frekvencija koristi se za dobivanje ulaznih podataka koji proizvode PWM signale pomoću usporedbe. Elektroničke tvrtke dizajniraju hardver posvećen njihovim proizvodima sa svojim standardima i protokolima što krajnjim korisnicima predstavlja izazov da rekonfiguriraju hardver prema svojim potrebama. Ovaj zahtjev za hardverom doveo je do rasta novog segmenta koji se može prilagoditi kupcu integrirani krugovi koji se mogu programirati na terenu zvani FPGA .

Modulacija širine impulsa (PWM)

Modulacija širine impulsa široko se koristi u aplikacijama komunikacije i upravljački sustavi . Modulacija širine impulsa može se generirati pomoću različitih pristupa u upravljačkim sustavima. Ovdje, u ovom članku, PWM se generira pomoću jezika za opis hardvera (VHDL) i implementira na FPGA. Implementacija PWM-a na FPGA može brže obraditi podatke, a arhitektura kontrolera može se optimizirati za prostor ili brzinu.

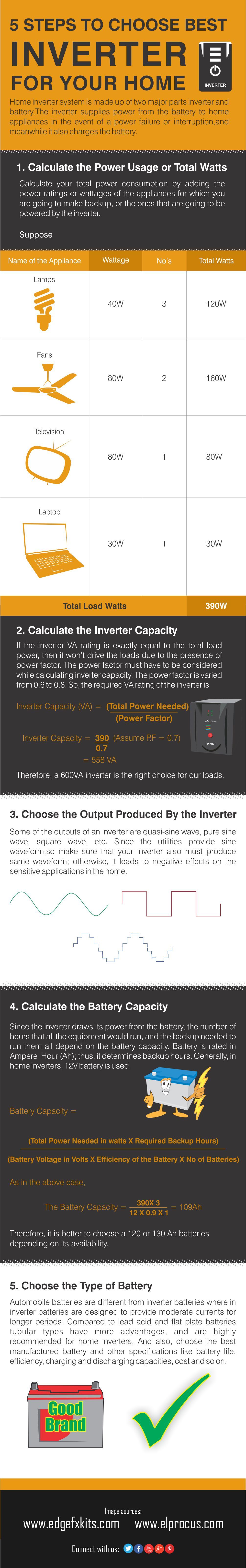

PWM je tehnika za osiguravanje logike '0' i logike '1' za kontrolirano vremensko razdoblje. To je izvor signala koji uključuje modulaciju njegovog radnog ciklusa za kontrolu količine snage koja se šalje na teret. U PWM-u, vremensko razdoblje kvadratnog vala održava se konstantnim, a vrijeme za koje signal ostaje VISOK varira.

PWM generira impulse na svom izlazu na takav način da je prosječna vrijednost VISOKA i NISKA proporcionalna proporcionalnom ulazu PWM-a. Radni ciklus signala može se mijenjati. PWM signal je kvadratni val konstantnog razdoblja s različitim radnim ciklusom. To jest, frekvencija PWM signala je konstantna, ali vremensko razdoblje signala ostaje visoko i varira kako je prikazano.

PWM signal

VHDL

VHDL je jezik koji se koristi za opisivanje ponašanja dizajni digitalnih sklopova . VHDL koriste industrije i akademici u svrhu simulacije digitalnih sklopova. Njegov se dizajn može simulirati i prevesti u obliku koji je pogodan za implementaciju u hardver.

PWM arhitektura

Da bi se proizveli ulazni podaci za generiranje PWM-a, koristeći brzi N-bitni brojač slobodnog rada, čiji se izlaz uspoređuje s izlazom registra i pohranjuje željeni radni ciklus uz pomoć usporedbe. Usporednik izlaz je postavljen na 1 kada su obje ove vrijednosti jednake. Ovaj izlaz za usporedbu koristi se za postavljanje RS zasuna. Signal preljeva s brojača koristi se za resetiranje zasuna RS. The izlaz zasuna RS daje željeni PWM izlaz. Ovaj signal preljeva također se koristi za učitavanje novog N-bitnog radnog ciklusa u Registar. PWM ima fiksnu frekvenciju i promjenjivi napon. Ova vrijednost napona mijenja se od 0V do 5 V.

PWM signal s promjenjivim radnim ciklusom

Osnovni PWM generira signale, što daje izlaz PWM-a, zahtijeva usporednik koji uspoređuje dvije vrijednosti. Prva vrijednost predstavlja kvadratni signal generiran s N brojačem bitova, a druga vrijednost predstavlja kvadratni signal koji sadrži informacije o radnom ciklusu. Brojač generira signal opterećenja kad god dođe do prelijevanja. Nakon što signal opterećenja postane aktivan, registar učitava novu vrijednost radnog ciklusa. Signal opterećenja koristi se i za resetiranje zasuna. Izlaz zasuna je PWM signal. To varira s promjenom vrijednosti radnog ciklusa.

Što je FPGA?

FPGA je polje programabilnih vrata. To je vrsta uređaja koja se široko koristi u elektroničkim sklopovima. FPGA su poluvodički uređaji koji sadrže programabilne logičke blokove i međusobne veze. Nakon proizvodnje može se programirati ili reprogramirati na potrebnu funkcionalnost.

FPGA

Osnove FPGA

Kada se proizvodi pločica i ako kao dio sadrži FPGA. To se programira tijekom proizvodnog procesa, a kasnije se može reprogramirati kako bi se stvorilo ažuriranje ili izvršile potrebne promjene. Ova značajka FPGA čini ga jedinstvenim od ASIC-a. Integrirani krugovi specifični za primjenu (ASIC) izrađeni su po mjeri za određeni projektni zadatak. U prošlosti su se FPGA koristili za razvoj dizajna niske brzine, složenosti i glasnoće, ali danas će FPGA lako pomaknuti barijeru performansi do 500 MHz.

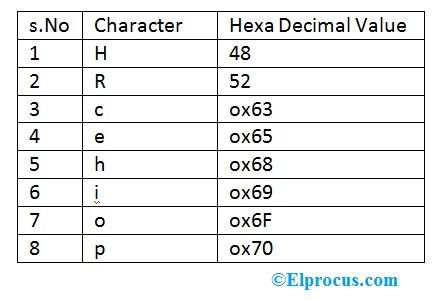

U mikrokontrolerima je čip dizajniran za kupca i oni moraju napisati softver i kompilirati ga u hex datoteku da bi se učitao na mikrokontroler. Ovaj se softver lako može zamijeniti jer je pohranjen u flash memoriju. U FPGA-ima ne postoji procesor za pokretanje softvera, a mi smo taj koji dizajnira sklop. FPGA možemo konfigurirati tako jednostavno kao AND ulaz ili složeni kao višejezgreni procesor. Da bismo stvorili dizajn, pišemo Hardware Description Language (HDL), koji je dvije vrste - Verilog i VHDL. Zatim se HDL sintetizira u bit datoteku pomoću BITGENA za konfiguriranje FPGA. FPGA pohranjuje konfiguraciju u RAM, odnosno konfiguracija se gubi kad nema povezivanja s napajanjem. Stoga se moraju konfigurirati svaki put kad se napajanje napaja.

Arhitektura FPGA

FPGA su gotovi silicijski čipovi koji se mogu električki programirati za implementaciju digitalnih dizajna. Prvi FPGA zasnovan na statičkoj memoriji nazvan SRAM koristi se za konfiguriranje i logike i međusobnog povezivanja pomoću niza konfiguracijskih bitova. Današnji moderni EPGA sadrži približno 3,30 000 logičkih blokova i oko 1100 ulaza i izlaza.

FPGA arhitektura

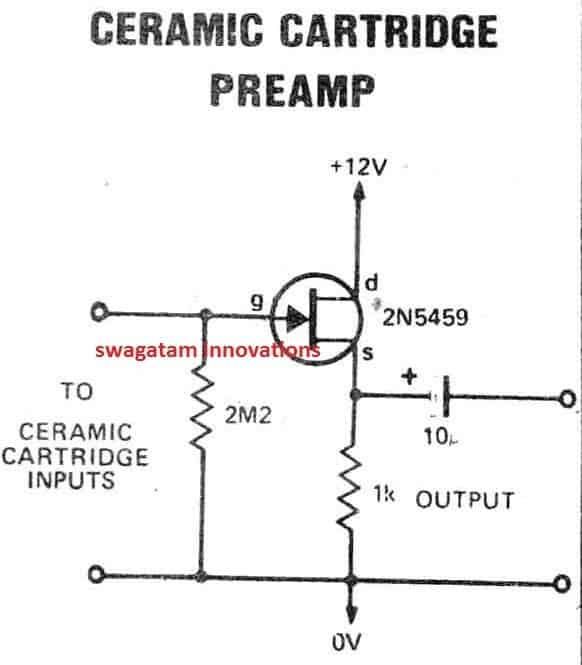

Arhitektura FPGA sastoji se od tri glavne komponente

- Programabilni logički blokovi, koji implementiraju logičke funkcije

- Programabilno usmjeravanje (međusobno povezivanje), koje provodi funkcije

- I / O blokovi, koji se koriste za uspostavljanje veza izvan čipa

Primjena PWM signala

PWM signali se široko koriste za upravljanje. Poput upravljanja istosmjernim motorima, upravljačkim ventilima, crpkama, hidraulikom itd. Evo nekoliko primjena PWM signala.

- Sustavi grijanja s sporim vremenima od 10 do 100 Hz ili više.

- Istosmjerni elektromotori 5 do 10KHz

- Napajanja ili audio pojačala od 20 do 200 KHz.

Ovaj članak govori o generiranje PWM signala s promjenjivim radnim ciklusom pomoću FPGA. Nadalje, za bilo kakvu pomoć u vezi s elektroničkim projektima ili nedoumice u vezi s ovim člankom možete nas kontaktirati komentirajući dolje navedeni odjeljak za komentare.