Glavni nedostatak kombinacijski krug je, ne koristi memoriju za spremanje sadašnjeg i prethodnog stanja. Stoga prethodno stanje ulaza nema utjecaja na trenutno stanje kruga. Dok sekvencijalni sklop ima memoriju, tako da izlaz može varirati ovisno o ulazu. Ova vrsta sklopova koristi prethodni ulaz, izlaz, sat i memorijski element. Ovdje memorijski elementi mogu biti zasun ili japanke. Sekvencijalni krugovi dizajnirani su raznim metodama kao što su upotreba ROM-a i preklopa, PLA-ovi, CPLD (složeni programibilni logički uređaj) , FPGA (Field Programmable Gate Array) . U ovom ćemo članku razgovarati samo o tome kako dizajnirati sekvencijalni krug pomoću PLA-a.

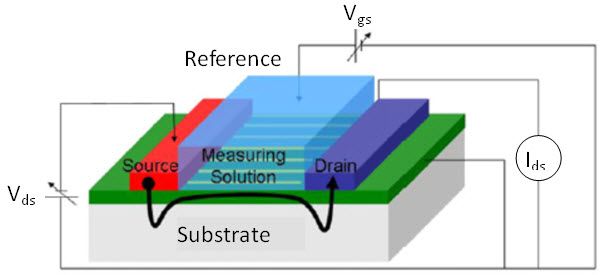

Blok dijagram sekvencijalnog kruga kako je prikazano dolje:

Blok dijagram sekvencijalnog kruga

Projektiranje sekvencijalnog kruga pomoću PLA-ova

Sekvencijalni krugovi može se realizirati pomoću PLA-a (programabilnih logičkih nizova) i japanki. U ovom dizajnu, dodjela stanja može biti važna jer upotreba dobrog dodjeljivanja stanja može smanjiti potreban broj izraza proizvoda, a time i potrebnu veličinu PLA. Pojam proizvoda definiran kao povezanost literala, gdje je svaki literal ili varijabla ili njegova negacija.

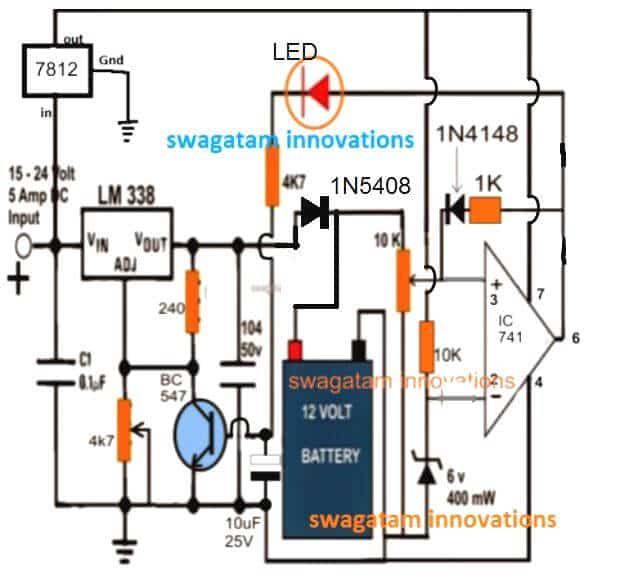

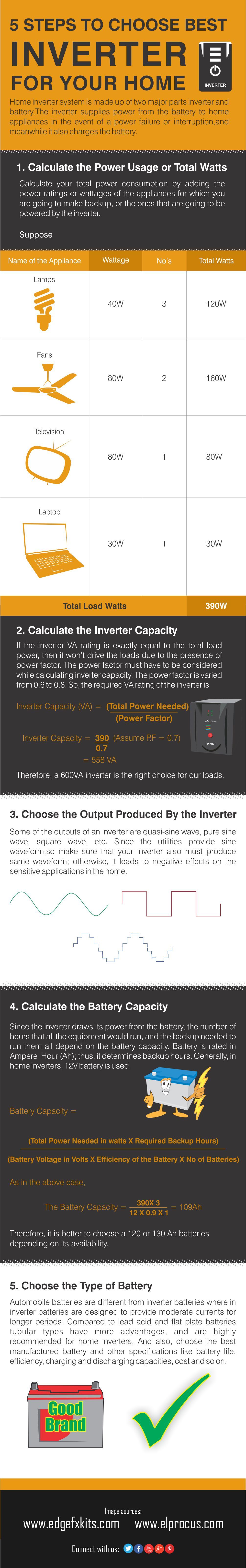

Razmotrimo stoga dizajn pretvarača koda. Tablica stanja prikazana dolje u tablici može se ostvariti korištenjem jednog PLA i tri Japanke kako je prikazano ispod slike. Ova konfiguracija sklopa vrlo je slična dizajnu baziranom na flip-flopu, osim što je ROM zamijenjen PLA prikladne veličine. Dodjela države vodi do dolje navedene tablice istine. Ova bi se tablica mogla pohraniti u PLA s četiri ulaza, 13 termina proizvoda i četiri izlaza, ali to bi nudilo malo smanjenu veličinu u usporedbi s ROM-om od 16 riječi.

| X Q1 Q2 Q3 | S D1 D2 D3 |

| 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 | 1 0 0 1 1 0 1 1 0 1 0 0 0 1 0 1 1 1 0 1 0 0 0 0 1 0 0 0 X X X X 0 0 1 0 0 1 0 0 1 1 0 0 1 1 0 1 0 1 1 0 1 0 0 0 X X X X X X X X |

Tablica: Tablica istine

PREDSTAVITI DRŽAVA

| SLJEDEĆA DRŽAVA X = 0,1 | PREDSTAVITI IZLAZ (Z) |

| DO | B C | 1 0 |

B C | D E I E | 1 0 0 1 |

D JE | H H H M | 0 1 1 0 |

H M | A A TO - | 0 1 1 - |

Tablica: Državna tablica

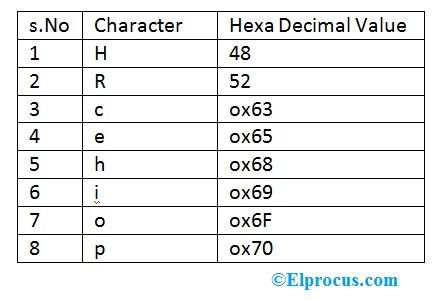

Projektiranje sekvencijalnih krugova pomoću PLA

Ulazne izlazne jednadžbe izvedene od Karnaugh Map

Ovdje, budući da postoji sedam stanja, potrebne su tri D japanke. Dakle, potreban je PLA krug s 4 ulaza i 4 izlaza. Ako se razmatra dodjela stanja pretvarača koda, rezultirajuća izlazna jednadžba i D flip-flop ulazne jednadžbe izvedene iz Karnaugh-a mogu se napisati sljedeće jednadžbe

D1 = Q1 + = Q2 '

D2 = Q2 + = Q2 '

D3 = Q3 + = Q1 Q2 Q3 = X ”Q1 Q3” = X Q1 ”Q2”

Z = X ”Q3” + X Q3

| X Q1 Q2 Q3 | S D1 D2 D3 |

- - 0 - - 1 - - - 1 1 1 0 1 - 0 1 0 0 - 0 - - 0 jedanaest

| 0 1 0 0 0 0 1 0 0 0 0 1 0 0 0 1 0 0 0 1 1 0 0 0 1 0 0 0

|

PLA tablica koja odgovara ovim jednadžbama dana je u gornjoj tablici. Ova se tablica može ostvariti korištenjem PLA s četiri ulaza, sedam pojmova proizvoda i četiri izlaza. Da bismo u početku provjerili rad gornjeg dizajna, pretpostavimo da su X = 0 i Q1Q2Q3 = 000. Ovo odabire retke - - 0- i 0 - - -0 u tablici, pa je Z = 0 i D1D2D3 = 100. Nakon aktivnog ruba sata, Q1Q2Q3 = 100. Ako je sljedeći ulaz X = 1, tada su odabrani retci - - 0 - i - 1- -, pa su Z = 0 i D1D2D3 = 110. Nakon aktivnog ruba sata, Q1Q2Q3 = 110.

Programabilni logički niz (PLA)

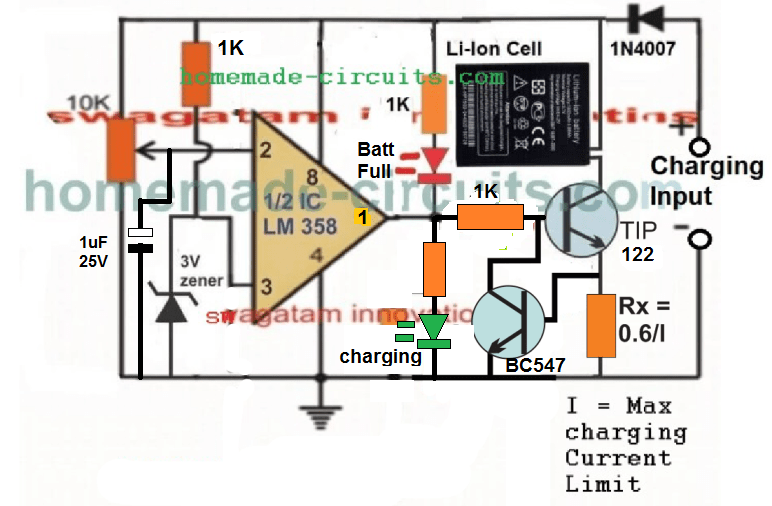

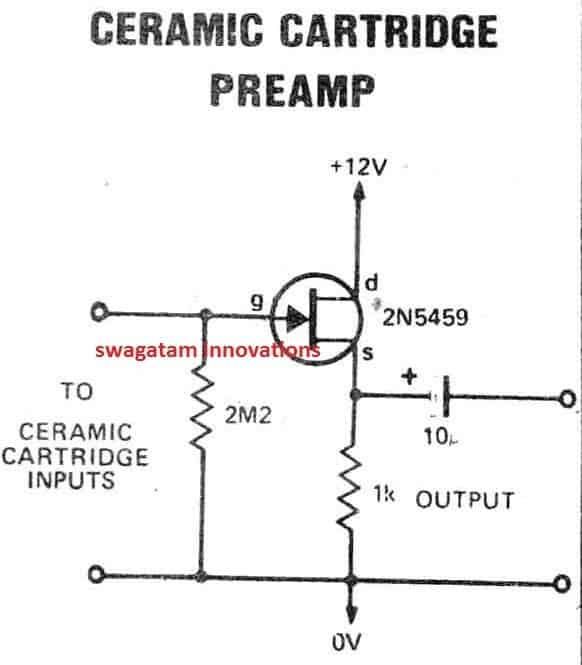

Programabilni logički niz je programabilni logički uređaj. Općenito se koristi za implementaciju kombinacijskih logičkih sklopova. PLA ima skup programabilnih I ravnina (I niz), koji se povezuju sa skupom programabilnih ILI ravnina (ILI niz), koji se zatim mogu privremeno dopuniti kako bi se dobio izlazni rezultat. Ovaj raspored omogućuje sintezu velikog broja logičkih funkcija u zbroj proizvoda (SOP) kanonski oblici. Jednostavan blok dijagram PLA dan je u nastavku.

Blok dijagram PLA

Glavna razlika između PLA i PAL (programabilna logika niza) je,

PLA: Oboje I ravnina i ILI ravnina mogu se programirati.

PAL: Programibilna je samo ravnina I, dok je ravnina ILI fiksna.

Za bolje razumijevanje PLA, ovdje razmatramo donji primjer.

Pokušajmo implementirati ove funkcije f1 i f2 dane su kao

Ulazi x1, x2, x3 i njihovi odgovarajući dopunjeni signali daju se u programabilnu ravninu AND, tamo ćemo dobiti izlaze ravni AND kao P1, P2, P3 nazvane minterme. Tada se ti signali daju na programabilnu ILI ravninu da proizvedu tražene izlazne funkcije f1 i f2 (zbroj proizvoda). Sljedeća slika opisuje implementaciju PLA na razini vrata za zadanu funkcionalnost.

Provedba PLA-a

Ovo je sve o dizajniranju sekvencijalnih krugova pomoću PLA. Smatramo da su vam podaci dani u ovom članku korisni za bolje razumijevanje ovog koncepta. Nadalje, bilo kakva pitanja u vezi s ovim člankom ili bilo kakva pomoć u provedba električnih i elektroničkih projekata , možete nam se obratiti komentirajući u odjeljku za komentare u nastavku. Evo pitanja za vas, Što znači sekvencijalni krug?